# Silicon Photonic Accelerated Memory Pooling For Efficient Compute Resource Allocation

Zhenguo Wu and Keren Bergman zw2542@columbia.edu

Lightwave Research Laboratory Columbia University, New York, NY

Aug 20th, 2025

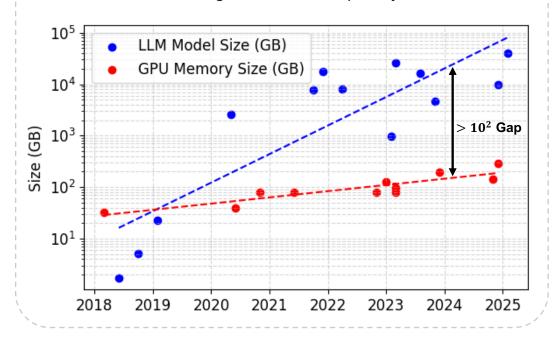

# Memory Challenges in Scaling Large Language Models

#### **GPU Memory Limitations**

- The growth rate of high-bandwidth memory (HBM) per GPU is much slower than the rapid scaling of Large Language Models (LLMs).

- The growing gap limits batch size scaling and adds distributed training/inference complexity.

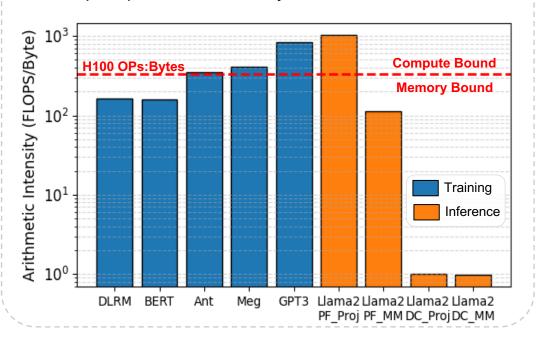

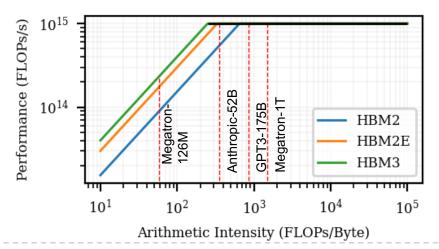

#### **Arithmetic Intensity Variations**

- LLM models exhibit diverse arithmetic intensities across workloads for training and inference, as well as between the prefill and decode stages of inference.

- Each workload (or stage) imposes unique demands on compute power and memory bandwidth.

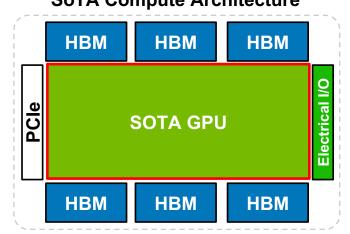

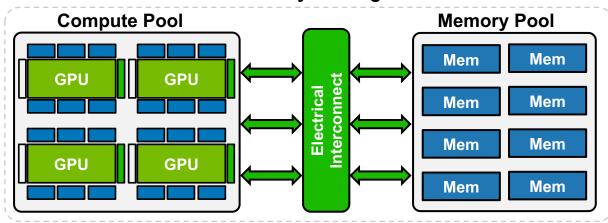

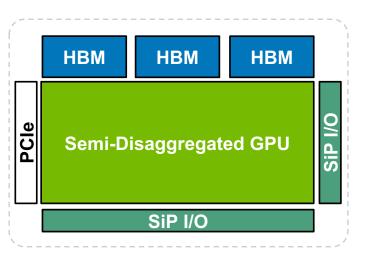

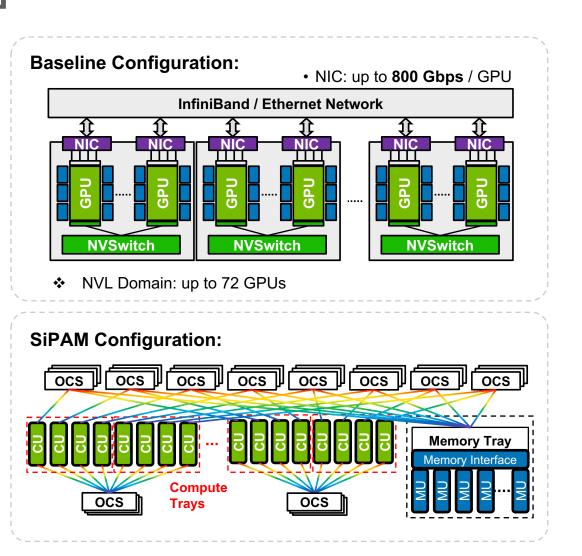

### **Current Compute & Memory Pooling Architecture**

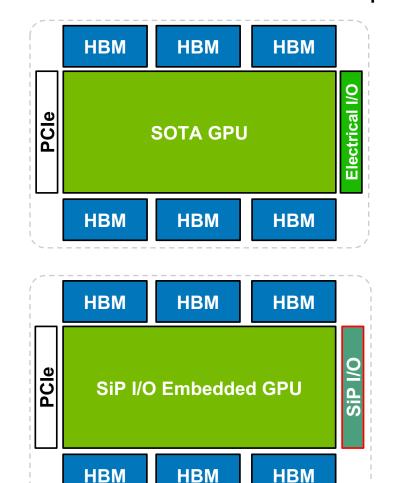

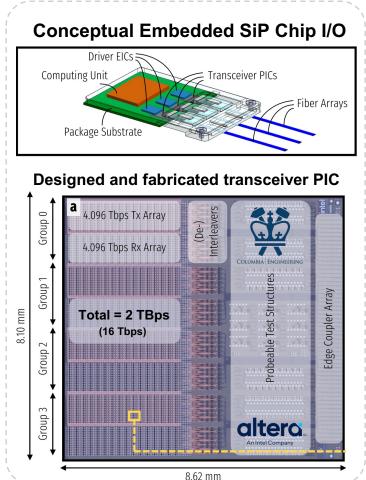

### SoTA Compute Architecture

#### **Current Memory Pooling Architecture**

- **❖** HBMs are placed around the periphery of the compute die using short-reach electrical I/Os.

- > HBM's wide I/O and high pin count requires short electrical traces, restricting it to areas near the compute die.

- Compute die's periphery length restricts the number of HBMs that can be integrated locally.

- Limited memory capacity scaling.

- Memory Pooling: compute pool connects to memory pool via a high-speed electrical interconnect.

- Local HBMs serve as high-bandwidth memory suppliers (lower capacity).

- Remote memory units (e.g., DDR, GDDR) act as capacity expanders via an electrically interconnected fabric.

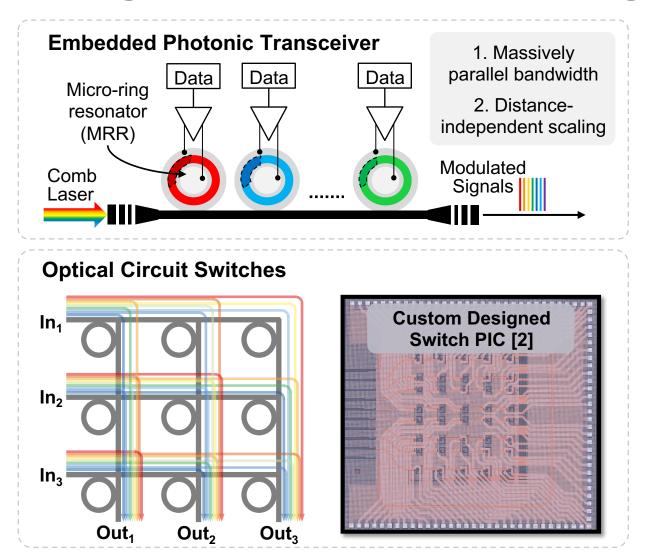

### **Enabling Silicon Photonic Technologies**

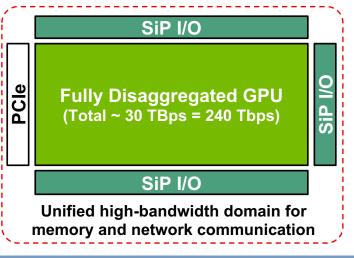

# **Expanding the Memory Pooling Design Space**

Compute die's *shoreline width* is used a critical resource.

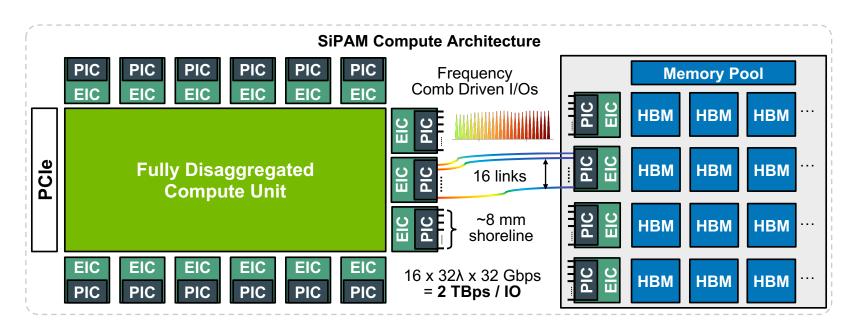

### SiPAM: Silicon Photonic Accelerated Memory-Pooling

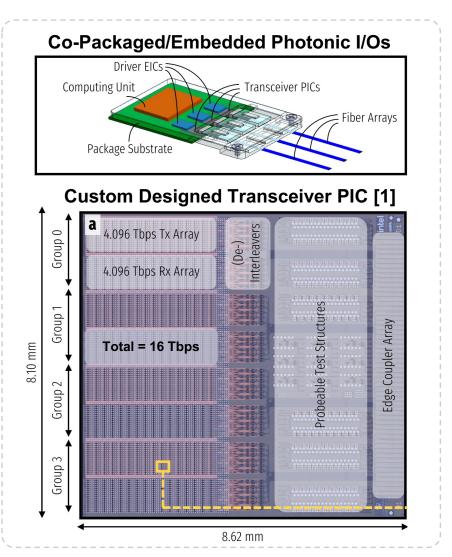

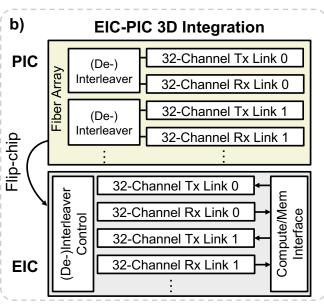

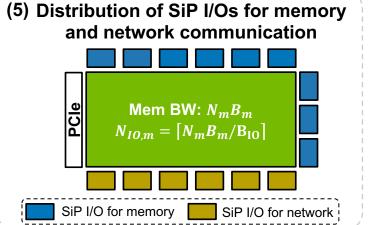

- ❖ SiP I/Os: 3D integrated EIC and PIC through flip-chip bonding

- Fach SiP I/O : 16 links × 32  $\lambda$  / link × 32 Gbps /  $\lambda$  = 2 TBps

- Number of integratable I/Os:  $N_{IO} = [W_D/W_{IO}]$

- $\succ W_D$  = Available compute die shoreline width

- $\rightarrow$   $W_{IO}$  = Edge width per SiP I/O

- Memory Pool: Optically Connected Multi-Stack HBM [3]

- Multiple HBMs connect to a single SiP I/O chiplet

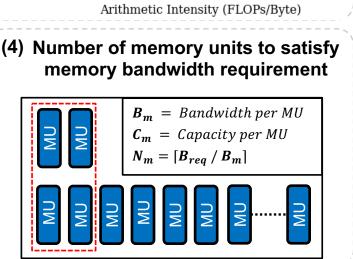

- Number of integratable MUs / IO:  $N_m = \lfloor B_{IO}/B_m \rfloor$

- $\triangleright$   $B_{IO}$  = SiP I/O bandwidth

- $\triangleright$   $B_m$  = MU bandwidth

### SiPAM: Silicon Photonic Accelerated Memory-Pooling

- Each SiP I/O can be flexibly allocated for high-speed memory access or network communication.

- One-shot reconfiguration per workload.

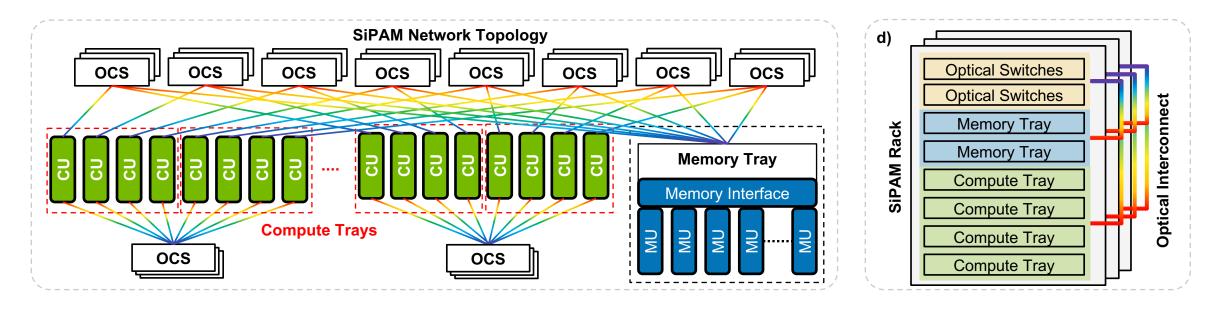

- SiPAC's physical design: replaces electrical packet switches (EPS) with optical circuit switches (OCS) in a BCube topology

- ➤ Intra-rack resource disaggregation model [4] for a bounded increase in memory latency.

- CXL is a promising memory semantic interconnect technology:

- > Increased memory latency can be mitigated by increasing CXL bandwidth when the memory system is fully loaded [5].

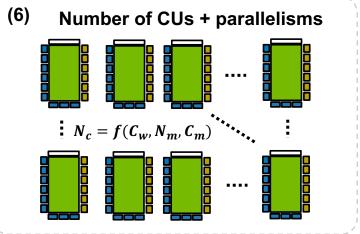

# **Optimization Methodology**

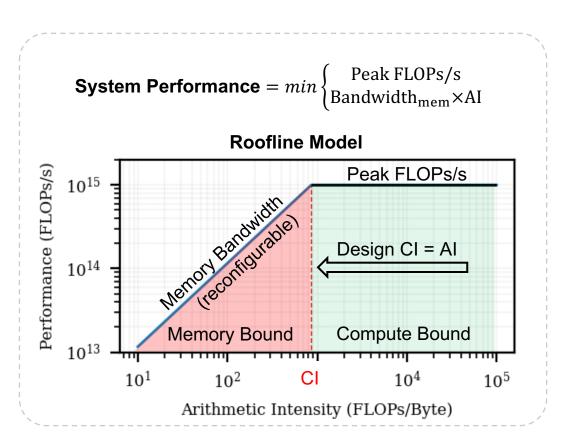

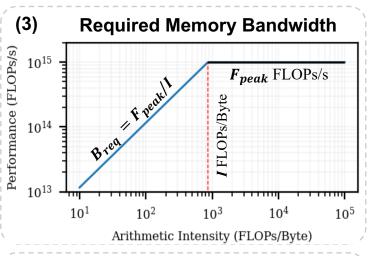

**Goal**: Determine the optimal configuration for **compute power**, **memory bandwidth**, and **capacity** for each workload.

#### Hardware

Compute Intensity (CI): # of required FLOPs per byte of data loaded to keep cores active.

$$CI = \frac{\text{Peak FLOPs/s}}{\text{Bandwidth}_{\text{mem}}} = \frac{\text{FLOPs}}{\text{Byte}}$$

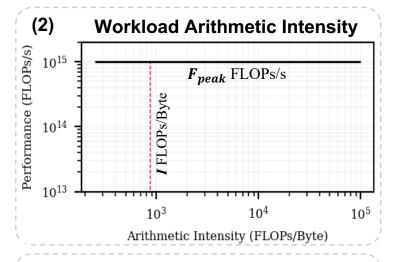

#### Workload

Arithmetic Intensity (AI): # of actual FLOPs performed for each byte of data loaded.

$$AI = \frac{\text{FLOPs}}{\text{Byte}}$$

### **Optimization Methodology**

**Goal**: Determine the optimal configuration for **compute power**, **memory bandwidth**, **capacity** for each workload.

# **Evaluation Setup – Calculon [6]**

#### **Workload & Configurations**

- Arithmetic Intensity: profiled using Calculon

- Capacity Requirement: profiled using Calculon

- Baseline Configuration:

- NVLink (scale-up) + InfiniBand (scale-out)

- **SiPAM Configuration:**

- SiPAC network

- Optimized # GPUs, memory capacity and bandwidth

# **Evaluation Setup – Calculon [6]**

#### **Hardware – Nvidia GPU Based**

| Single CU   | FP16<br>TFLOPs | Mem Cap<br>(GB) | Mem BW<br>(TBps) |

|-------------|----------------|-----------------|------------------|

| Nvidia A100 | 312            | 40              | 1.5              |

| Nvidia H100 | 1000           | 80              | 3                |

| Nvidia B100 | 3500           | 192             | 8                |

| SiPAM*      | 3500           | Up to 720       | Up to 30         |

❖ Cluster Size: up to 1024 GPUs

| Cluster of<br>1024 CUs | FP16<br>PFLOPs | Mem Cap<br>(TB) | Mem BW<br>(PBps) |

|------------------------|----------------|-----------------|------------------|

| Nvidia A100            | 320            | 41              | 1.5              |

| Nvidia H100            | 1024           | 82              | 3.1              |

| Nvidia B100            | 3584           | 197             | 8.2              |

| SiPAM*                 | 3584           | Up to 737       | Up to 31         |

<sup>\*</sup> Assuming B100 as CU and HBM3E as MU

ocs

Compute

**Trays**

ocs

**Memory Tray**

# **Simulation Results - Training**

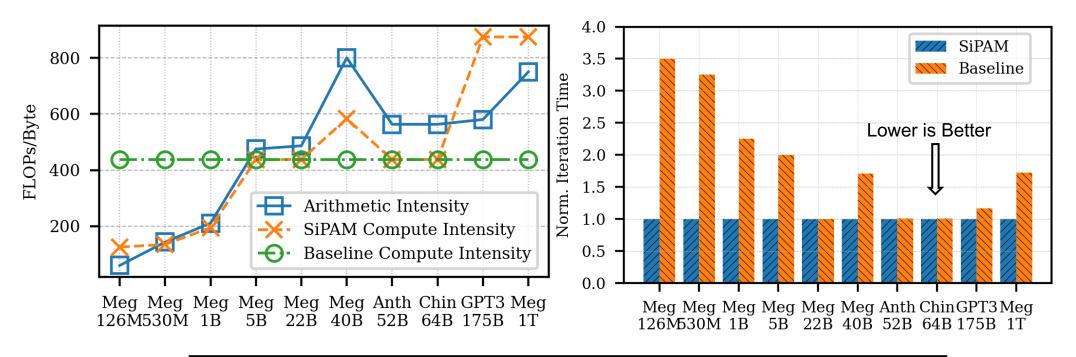

- ❖ Workloads: Megatron-126M/5B/22B/40B/1T, Anthropic 52B, Chichilla-64B, GPT3-175B (Training)

- ❖ Baseline: Up to 256 B100 GPUs each with fixed 192 GB HBM memory @ 8 TBps total memory bandwidth

- ❖ SiPAM: Up to 256 GPUs, with compute, memory bandwidth, and capacity optimized based on each workload

- a) SiPAM tracks arithmetic intensity closely, while the baseline remains constant

- o) SiPAM improves training time by up to **3.5x**

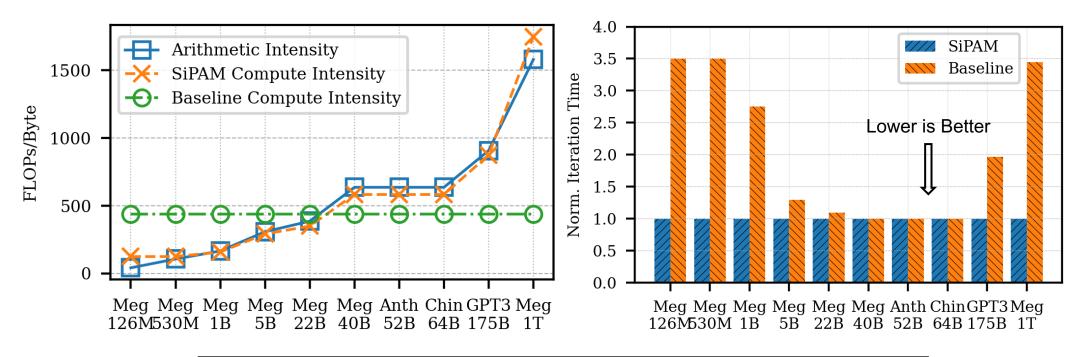

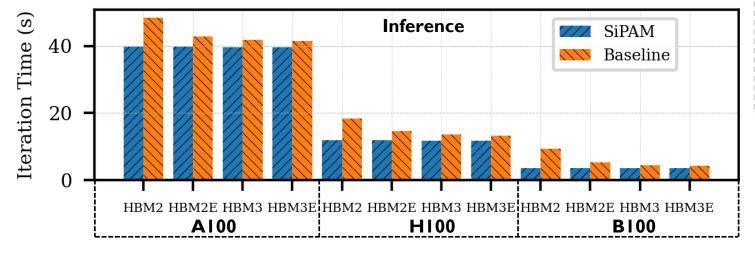

### **Simulation Results - Inference**

- ❖ Workloads: Megatron-126M/5B/22B/40B/1T, Anthropic 52B, Chichilla-64B, GPT3-175B (Inference)

- ❖ Baseline: Up to 64 B100 GPUs each with fixed 192 GB HBM memory @ 8 TBps total memory bandwidth

- ❖ SiPAM: Up to 64 GPUs, with compute, memory bandwidth, and capacity optimized based on each workload

- a) SiPAM tracks arithmetic intensity closely, while the baseline remains constant

- b) SiPAM improves inference time by up to **3.5x**

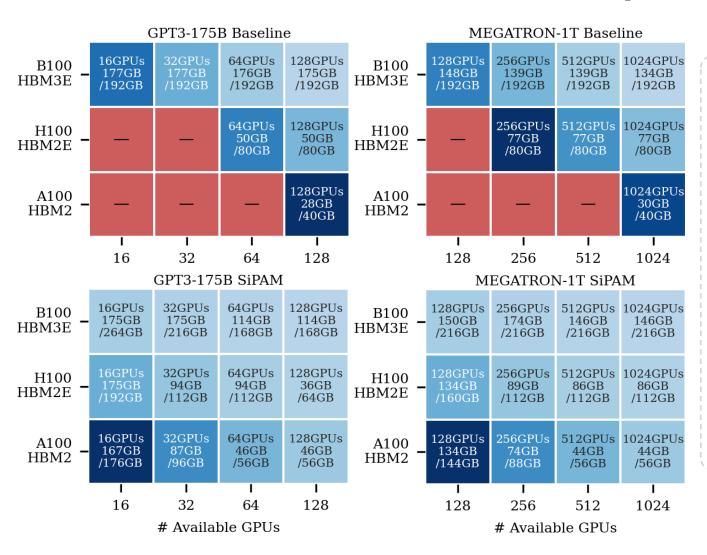

### Performance Under Limited Compute Resource

#### **❖** Configurations:

- ❖ Workload: GPT3-175B and Megatron-1T

- Red cells: no feasible parallelization strategy

- Darker color: higher iteration time

- Takeaway: SiPAM consistently enables feasible deployment of larger models under constrained GPU resources

- SiPAM flexibly allocates memory capacity and bandwidth.

- For a fixed GPU-HBM combination, iteration time decreases as the number of available GPUs increases.

- For a fixed number of GPU, newer GPU generations yield lower iteration time.

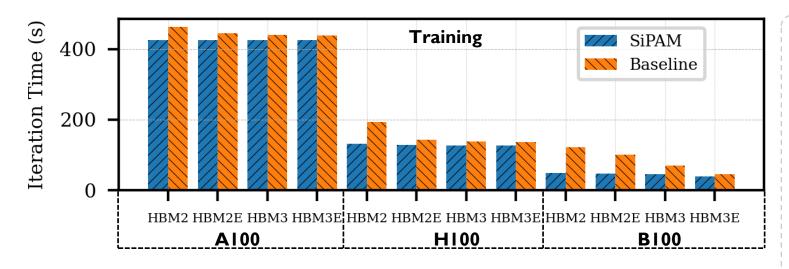

# **Compute & Memory Technology Scaling**

#### **❖** Configurations:

Workload: GPT3-175B

Network size: 128 GPUs

Cross GPU-HBM pairing

- Takeaway: SiPAM consistently outperforms the baseline by allocating the needed compute and memory resources

- Newer GPU generations outperform earlier ones.

- For each GPU generation, performance improves as memory generation advances.

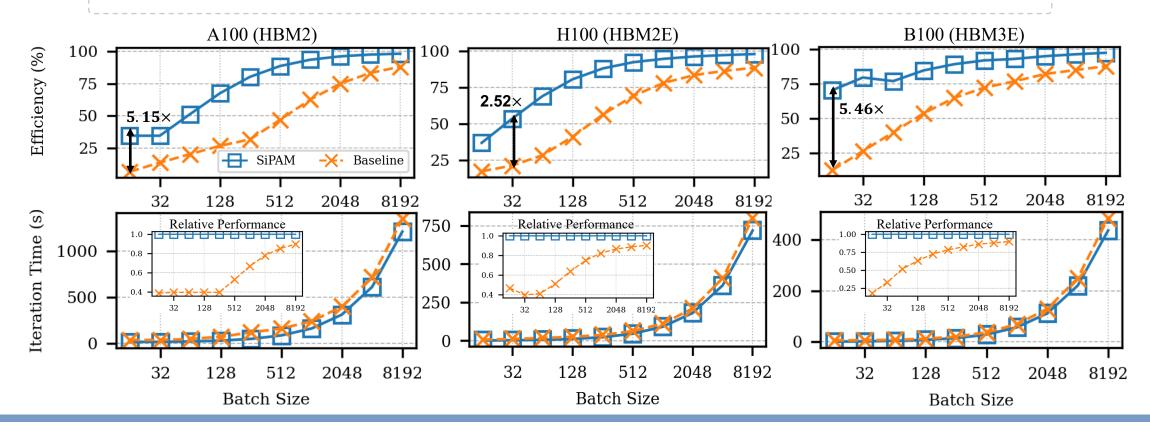

# **System Efficiency Analysis**

#### **❖** Configurations:

❖ Workload: Megatron-1T

System Efficiency =  $\frac{T_{compute}}{T_{total}}$

- Metrics: System Efficiency & Iteration Time (inset shows relative performance)

- SiPAM consistently outperforms the baseline in both efficiency and iteration time.

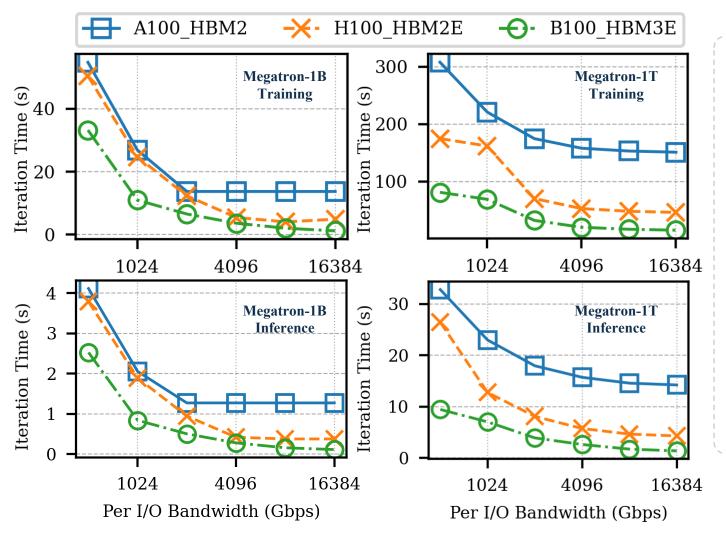

### SiP I/O Bandwidth Scaling

#### **❖** Configurations:

- ❖ Workload: Megatron-1T & Megatron-1T

- ❖ Per I/O Bandwidth: 512 Gbps to 16 Tbps

- Total injection bandwidth / GPU:

- ❖ A100/H100: 6 Tbps to 192 Tbps

- ❖ B100: 7.6 Tbps to 240 Tbps

- ❖ Takeaway: Newer GPU generations with higher compute capability require greater memory bandwidth to achieve continued performance scaling.

- ❖ A100 on Megatron-1B: performance plateaus

- Compute throughput becomes saturated

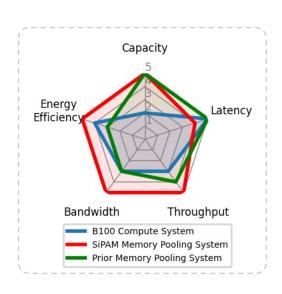

### Conclusion

- Problems addressed: memory capacity & bandwidth bottlenecks in AI/ML

- Design:

- Direct photonic integration along the perimeter of the compute die

- Unified high-bandwidth communication domain

- Optimization: co-designed roofline-model based allocation algorithm

- Results:

- Showed up to 3.5x faster iteration time

- Highlights the critical need for bandwidth scaling in next-generation compute.

#### • Future Works:

- Cost and power modeling

- Capture network demand in addition to memory demand

### **Acknowledgement**